ASML and High-NA EUV: Why 2027 is the Inflection Year

ASML’s High-NA EUV is real but late: expect risk runs in 2027 and a revenue ramp through 2028–29, as Intel leads and memory pilots broaden globally.

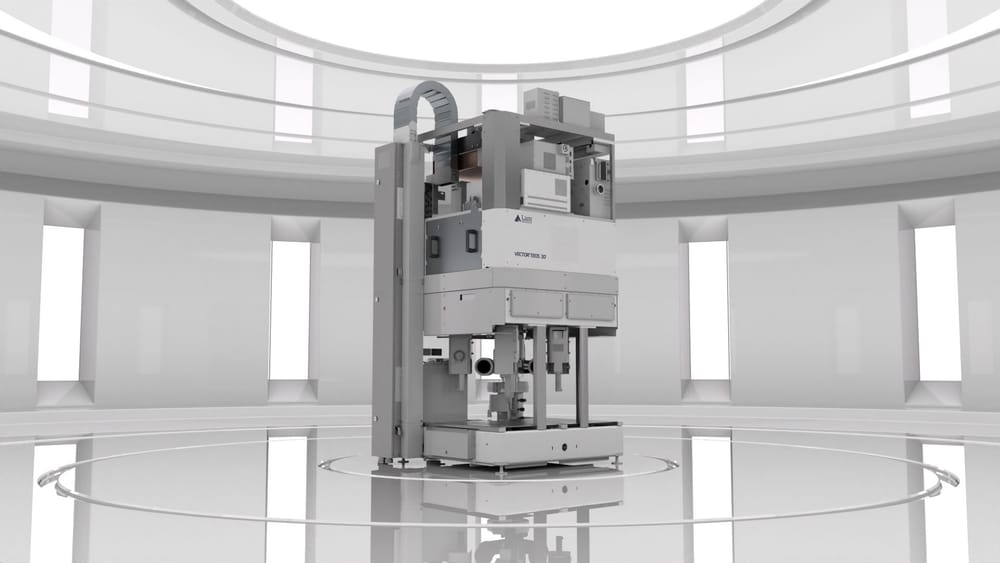

ASML’s next act has a name—High-NA EUV—and a price tag that would make even capital-heavy chipmakers blink. At roughly €350 million per scanner, the 165-ton TWINSCAN EXE:5200B is the most expensive machine on the fab floor. It promises up to 40% finer features than today’s EUV tools and a path to denser, faster chips. The question for investors is when that promise turns into revenue at scale. The short answer: not in 2025–26; the real ramp looks late-decade, with meaningful contributions beginning in 2027 and building through 2028–29.

Pieces of the puzzle are clicking into place. ASML shipped early High-NA systems and opened a joint readiness lab with Belgium’s imec so customers and materials suppliers can debug pellicles, masks, resists, and metrology before products hit high-volume manufacturing. Management has already recognized revenue on at least one High-NA tool in the June quarter, a reminder that the book-to-bill is turning from slideware into shipments. But these are still beachhead placements and ecosystem build-out, not a volume wave.

On the customer side, the first tangible proof point for production came from memory, not logic. SK hynix, chasing leadership in AI-centric DRAM, assembled what it calls the industry’s first “commercial” High-NA system at its M16 fab in Icheon. That installation underscores how memory makers—hungry to simplify multi-patterning and push cell scaling—may be early adopters, though even for DRAM the initial use will skew toward process development before bleeding into volume nodes.

Logic is the bigger prize, and here the road forks. Intel has nailed its colors to the mast: 14A will use High-NA, with risk production guided for 2027 and volume in 2028. Intel has also warned that the node will be more expensive than 18A precisely because of High-NA’s tool costs—another reason management says it wants sizable external foundry customers to underwrite the economics. The intent is clear, but the calendar remains tight.

TSMC, by contrast, is openly taking its time. The foundry giant says it can deliver A16 in the second half of 2026—and even A14 in 2028—without High-NA, leaning on low-NA EUV, backside power, and design-technology co-optimization. Executives keep repeating a simple litmus test: adopt High-NA only when the technical and economic case beats the alternatives. For ASML, that stance means near-term logic demand is likely gated by Intel and selected memory use, with broader uptake from TSMC arriving closer to the turn of the decade.

ASML itself has telegraphed a measured glidepath. Capacity planning calls for ramping High-NA output to roughly 20 systems per year by 2027–28, aligning with customers’ risk-to-HVM windows. That doesn’t sound like a tidal wave, but each system carries an outsize revenue punch compared with today’s low-NA EUV, and a growing installed base pulls through lucrative service and upgrades. In other words, even a dozen-plus tools can move the P&L.

Between now and the ramp, watch three markers. First, the cadence of 5200B shipments and site acceptances—ASML’s second-half logistics and customer-site installs will show whether the supply chain can stage these giants reliably. Second, ecosystem readiness—imec’s program on resists, pellicles, and inspection needs to keep pace so yield isn’t the long pole. Third, customer disclosure—concrete tape-out timelines from Intel’s 14A and any early DRAM nodes will convert “tool on floor” headlines into wafers out the door. Each of these has progressed, but none has flipped the “volume” switch yet.

Investors should also keep the competitive frame in view. High-NA is not the only way to shrink; TSMC’s preference to stay on low-NA EUV longer is a reminder that design rules, backside power, and advanced packaging can offset raw lithography advantages for a time. But once one leading-edge logic player demonstrates stable yields and cost on High-NA, copycat risk works in ASML’s favor. The company remains the sole source for the technology, and the move from pilot to production multiplies revenue per fab as additional scanners follow the first install.

So when does High-NA “really ramp”? The inflection to watch is 2027: multiple logic programs entering risk, memory experimenting beyond line-item R&D, and ASML’s factory output approaching its 20-tools-per-year target. The steeper revenue slope should appear in 2028–29 as Intel’s 14A moves toward high volume and as late-adopting logic and DRAM begin to qualify their own flows. Until then, the story is about placements, ecosystem maturation, and the expensive but necessary groundwork for the next phase of Moore’s Law. For ASML, that’s still a favorable setup: long-lead tools, anchored demand, and a ramp that—when it comes—arrives with the kind of average selling price only one company in the world can command.

Author

Investment manager, forged by many market cycles. Learned a lasting lesson: real wealth comes from owning businesses with enduring competitive advantages. At Qmoat.com I share my ideas.